# **READ ONLY MEMORY**

(ROM)

# SYED HASAN SAEED

hasansaeedcontrol@gmail.com

https://shasansaeed.yolasite.com

#### ROM

- In ROM Binary information is stored permanently.

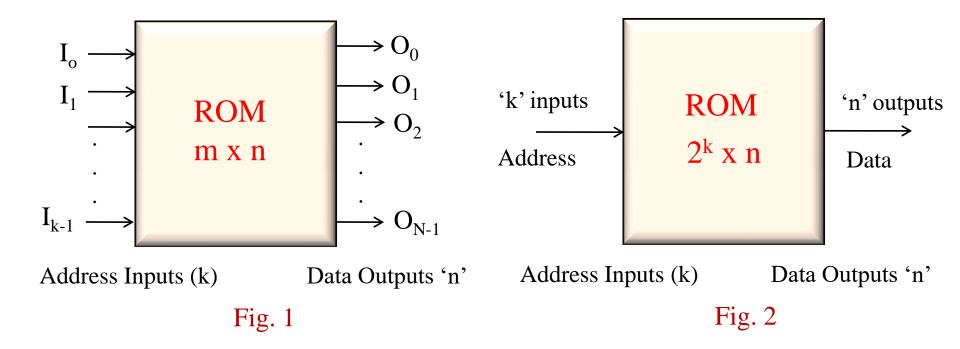

- Block diagram of ROM (size m x n ) is shown in fig.1, where 'm' is the number of locations and 'n' is the number of bit words that can stored in each locations.

### **ROM**

• There are 'k' number of address lines to access 'm' locations.

$$m = 2^k$$

- 'n' is the data output lines. This gives the data bits of the stored word selected by the address.

- Therefore for implementation of 'k' variables and 'n' outputs then the size of ROM is represented by  $2^k$  x n as shown in fig.2. this will generates all possible  $2^k$  minterms.

- ROMs are designed only for reading the stored informations.

- ROM does not have write operation i.e user cannot write any information.

- ROM is used to store fixed information like instructions, look up tables etc.

### **ROM**

- ROMs are programmed at the time of manufacturing.

- ROMs are costly.

- ROMs can be used for the implementation of combinational circuits

#### EXAMPLE 1

The following memory units are specified by the number of words times the number of bit per word. How many address lines and input-output data lines are required in each case.

Reference: Moris Mano

$$4K=2^2 \times 2^{10}=2^{12}$$

$4K \times 16$  can be written as  $2^{12} \times 16$

Therefore, there are 12 address lines and 16 data lines.

Total input-output lines = 12+16=32

$$1 G = 2^{30}$$

$$2G = 2 \times 2^{30} = 2^{31}$$

No. of Address line  $2G \times 8 = 2^{31} \times 8$

$$2G \times 8 = 2^{31} \times 8$$

Therefore, there are 31 address lines and 8 data lines.

Total input-output lines = 31+8=39

$$1 M = 2^{20}$$

$$16M = 2^4 \times 2^{20} = 2^{24}$$

16M x 32 can be written as

No. of Address line

$$16M \times 32 = 2^{24} \times 32$$

Therefore, there are 24 address lines and 32 data lines.

Total input-output lines = 24 + 32 = 56

Since,

$$1K=1024=2^{10}$$

$$256K = 2^8 \times 2^{10} = 2^{18}$$

No. of Address line

$256K \times 64$  can be written as  $2^{18} \times 64$

Therefore, there are 18 address lines and 64data lines.

Total input-output lines = 18 + 64 = 82

# **EXAMPLE 2**: Give the number of bytes stored in the memories listed in example 1. **SOLUTION**:

(i) 4K x 16

A byte is equivalent to 8 bits.

No. of 16 bit words =  $4K = 4 * 1024 = 2^{12} = 4096$

Memory Size = No. of words \* word size = 4096 \* 16 bit = 65536 bits

(Output is 16 i.e. 2 bytes)

Memory size =65536 / 8 = 8192 bytes = 8kB

(ii) 2G x 8

A byte is equivalent to 8 bits.

No. of 8 bit words =  $2G = 2G = 2 \times 2^{30} = 2^{31} = 2,147,483,648$

Memory Size = No. of words \* word size = 2,147,483,648 \* 8 bit = 17179869184 bits

(Output is 8 i.e. 1 bytes)

Memory size = 17179869184 / 8 = 2,147,483,648 = 2GB

A byte is equivalent to 8 bits.

No. of 16 bit words =

$$2^4 \times 2^{20} = 2^{24} = 16777216$$

Memory Size = No. of words \* word size = 16777216 \* 32 bit = 536870912 bits (Output is 32 i.e. 4 bytes)

Memory size =

$$536870912 / 8 = 67108864$$

bytes =  $64$  MB

Alternate 1:

$$16M = 2^{24}$$

$$16 \text{ M x } 32 = 2^{24} * 4 * 8 = 2^{24} * 2^{2} * 8 = 2^{26} * 8$$

No. of Bytes stored =

$$2^{26}$$

= 67108864 bytes = 64 MB

$$256K x 64$$

Memory Size = No. of words \* word size =  $256 k * 8B$

$$= 2048 \text{ kB} = 2 \text{ MB}$$

# TYPES OF ROM

- ➤ Mask Programmed ROM (MROM)

- ➤ Programmable Read Only Memory (PROM)

- Erasable Programmable Read Only Memory (EPROM)

- $\triangleright$  E<sup>2</sup>PROM

# **ADVANTAGES OF ROM**

- Low Cost

- High Speed

- Flexibility in system designed

- ROM is non-volatile memory.

## APPLICATIONS OF ROM

- It is used for the implementation of combinational circuits.

- It is used for the implementation of sequential circuits.

- Used for look up tables.

- Used for storage purpose of microprocessor program.

- It is suitable for the LSI manufacturing process.

- Used in function generators.

### INTERNAL STRUCTURE OF ROM

18-Apr-19

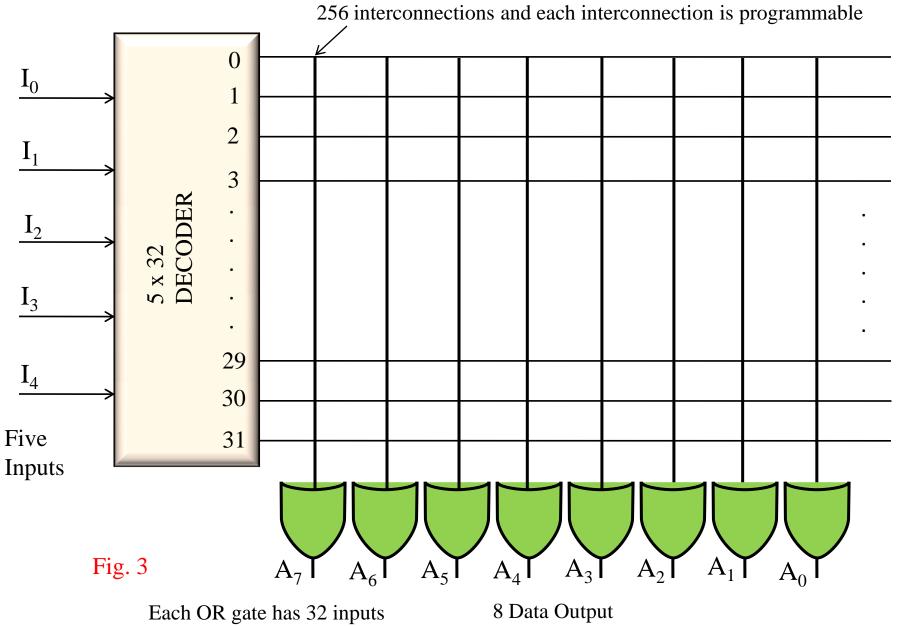

#### **EXAMPLE:** Consider 32 x 8 ROM.

- It consists of 32 words of 8 bits each.

- To access 32 locations (addresses) there are 5 input lines (m = 32, m =  $2^5$ , k = 5) which forms the binary numbers equivalent to 0 to 31.

- Fig.5 shows the internal logic of a ROM.

- The five inputs are decoded into 32 different outputs with the help of a 5 x 32 decoder and each output of the decoder represent a memory address.

- The 32 outputs of the decoder are connected to each of the eight OR gates. It means that each OR gate having 32 inputs.

- There are 8 OR gates and each OR gate has 32 connections, therefore total internal connections will be  $32 \times 8 = 256$

- In general '2<sup>k</sup> x n' ROM will have 'k x 2<sup>k</sup>' decoder and 'n' OR gates.

- Each OR gate has 2<sup>k</sup> inputs, which are connected to each of the outputs of the decoder.

- All 256 intersections are programmable.

- A programmable connection between two lines is equivalent to a switch which is either turned ON or OFF. ON means two lines are connected with each other and OFF means two lines are not connected.

- ROM truth table is shown in fig.4

- Truth table shows that there are 5 inputs and 8 outputs.

- There are 32 locations (addresses) and each location stored 8 bits word.

- '0' in truth table indicates there is no connection and '1' indicates a connection.

## TRUTH TABLE:

| Location No. | Inputs |       |       |                |       | Outputs |       |       |       |       |       |       |       |

|--------------|--------|-------|-------|----------------|-------|---------|-------|-------|-------|-------|-------|-------|-------|

|              | $I_4$  | $I_3$ | $I_2$ | $\mathbf{I}_1$ | $I_0$ | $A_7$   | $A_6$ | $A_5$ | $A_4$ | $A_3$ | $A_2$ | $A_1$ | $A_0$ |

| 0            | 0      | 0     | 0     | 0              | 0     | 1       | 0     | 0     | 1     | 0     | 0     | 1     | 1     |

| 1            | 0      | 0     | 0     | 0              | 1     | 0       | 0     | 0     | 1     | 1     | 1     | 0     | 1     |

| 2            | 0      | 0     | 0     | 1              | 0     | 1       | 0     | 1     | 1     | 0     | 0     | 0     | 1     |

| 3            | 0      | 0     | 0     | 1              | 1     | 1       | 0     | 0     | 0     | 1     | 1     | 1     | 0     |

| <br>         |        |       |       |                |       |         |       |       |       |       |       |       |       |

| <br>         |        |       |       |                |       |         |       |       |       |       |       |       |       |

| 29           | 1      | 1     | 1     | 0              | 1     | 1       | 0     | 0     | 0     | 1     | 0     | 1     | 0     |

| 30           | 1      | 1     | 1     | 1              | 0     | 0       | 1     | 1     | 1     | 0     | 0     | 0     | 1     |

| 31           | 1      | 1     | 1     | 1              | 1     | 0       | 1     | 1     | 0     | 0     | 0     | 1     | 1     |

# INTERNAL STRUCTURE OF 32 x 8 ROM

256 interconnections and each interconnection is programmable, 0  $I_0$ 2 3 5 x 32 DECODER  $I_3$ 0 29 30 0 Five 31 Inputs Fig. 3

Each OR gate has 32 inputs

8 Data Output

# THANK YOU